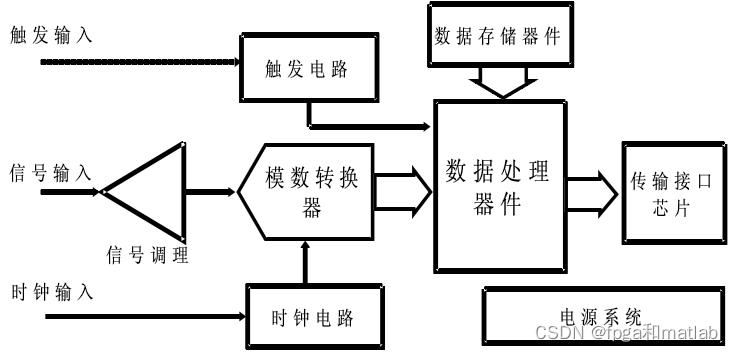

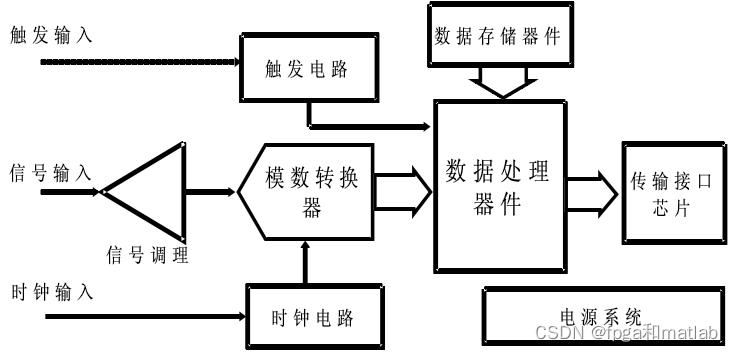

���ٔ�(sh��)��(j��)�ɼ���܊�������I(l��ng)�������V���đ�(y��ng)������������ٔ�(sh��)��(j��)�ɼ�ϵ�y(t��ng)���Ԅ�(d��ng)��������늚�y(c��)����������|(zh��)��̽�������պ���ȹ��̌�(sh��)�`�������O��V���đ�(y��ng)�á���Ό�(du��)���ٵ���̖(h��o)�M(j��n)�Ќ�(sh��)�r(sh��)�ɼ�����(sh��)�r(sh��)�惦(ch��)������C��̖(h��o)���Gʧ������ԝM�㹤�I(y��)�F(xi��n)��(ch��ng)����Ҫ������һֱ�Ǹ��ٔ�(sh��)��(j��)�ɼ�ϵ�y(t��ng)�о���һ��(g��)��Ҫ���������(sh��)��(j��)�ɼ�ϵ�y(t��ng)����̖(h��o)�c��Ϣ̎��ϵ�y(t��ng)�в���ȱ�ٵ���Ҫ�M�ɲ��֣�ͬ�r(sh��)Ҳ��ܛ���o���ϵ�y(t��ng)�еĺ���ģ�K�����ٔ�(sh��)��(j��)�ɼ�ϵ�y(t��ng)��Ҫ�������ׂ�(g��)���֣�ģ�M��̖(h��o)�{(di��o)���·��ģ��(sh��)�D(zhu��n)�Q�����������(sh��)��(j��)̎������������(sh��)��(j��)�惦(ch��)�����������r(sh��)��·�����|�l(f��)�·���������ݔ�ӿ�оƬ���Դϵ�y(t��ng)�ȣ���D1��ʾ�������

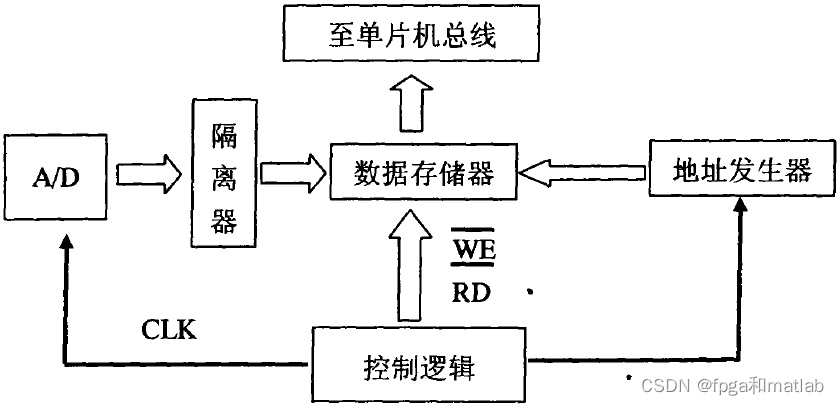

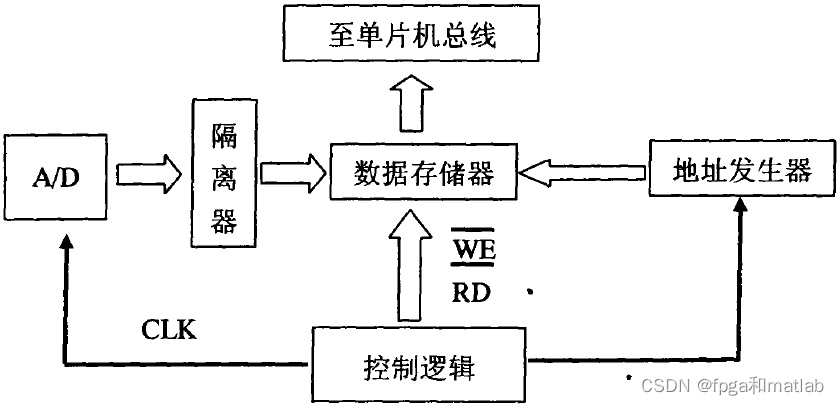

���������ģ�M��̖(h��o)�{(di��o)���·���Á팢ģ�M��̖(h��o)�Ŵ��{(di��o)����ADC�IJɘ�����֮��(n��i)�����@�Ӽ��ܳ�ְl(f��)�]ADC�����ܣ����ܱ��C�ɘӔ�(sh��)��(j��)���������������ADC�Ǹ��ٔ�(sh��)��(j��)�ɼ�ϵ�y(t��ng)�ĺ�����������ģ�M��̖(h��o)ݔ����������(sh��)����̖(h��o)ݔ�����������(sh��)��(j��)̎�������кܶ�N����������Ը���(j��)��(sh��)�H�IJ�ͬ��Ҫ�M(j��n)���x��(sh��)��(j��)�惦(ch��)������Ҫ���ڴ惦(ch��)��(sh��)��(j��)����������M(j��n)���@ʾ���طź͔�(sh��)��(j��)̎���Ȳ���������r(sh��)��·�DZ��^��Ҫ�ģ��r(sh��)犵ķ�(w��n)���Ժ;��_�ԛQ������(sh��)��(j��)�ɼ��ĽY(ji��)����������һ��������džΪ�(d��)�O(sh��)Ӌ(j��)��(w��n)���ĕr(sh��)��·������|�l(f��)�·��(sh��)�F(xi��n)�ⲿ��(du��)��(sh��)��(j��)�ɼ��l�ʺʹΔ�(sh��)�Ŀ������������ݔ�ӿ����ڌ���(sh��)��(j��)��ݔ�oӋ(j��)��C(j��)�M(j��n)�к�̎�����������Æ�·����A/D�D(zhu��n)�Q���Լ��惦(ch��)����(g��u)�ɴ��вɼ�ϵ�y(t��ng)ϵ�y(t��ng)��D��D2��ʾ:

���Æ�·����AD�D(zhu��n)�Q�����ٴ惦(ch��)�·�혋(g��u)���ִ��вɼ�ϵ�y(t��ng)�������ϵ�y(t��ng)�IJɘӾ͌��ڌ�(sh��)�r(sh��)�ɘ������m�����κ���ʽ����̖(h��o)���Σ��؏�(f��)�Ļ��؏�(f��)��������δεĻ��B�m(x��)�ġ����������вɘ��c(di��n)���ԕr(sh��)�g��������������ڌ�(sh��)�F(xi��n)�����@ʾ����������Dz��Æ�Ƭ����A/DоƬ���ٴ惦(ch��)����������(hu��)������ϵ�y(t��ng)�_�l(f��)�ɱ����ͬ�r(sh��)ϵ�y(t��ng)�IJɘ��ʾ��ܵ�A/D�D(zhu��n)�Q������D(zhu��n)�Q�����Լ��惦(ch��)�������ٶȵ������������������ͨ����(sh��)��(j��)�ɼ�ϵ�y(t��ng)�IJɼ��ٶ����������텢��(sh��)�����ƣ����y�ٴ����������D(zhu��n)�Q�ٶȡ�

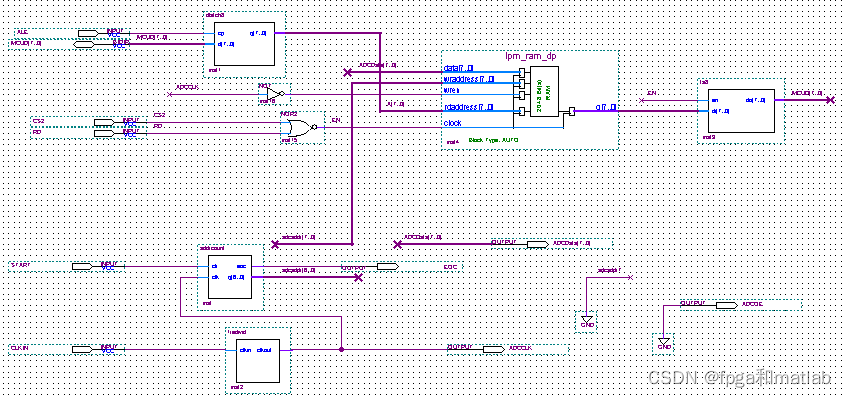

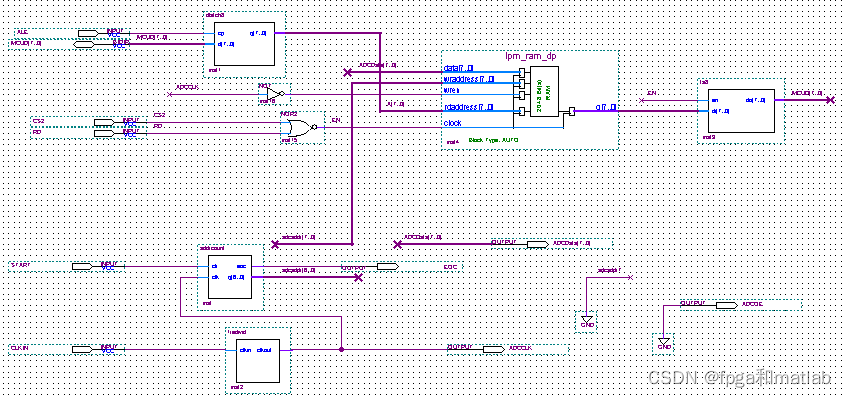

�����wFPGA�Y(ji��)��(g��u)������ʾ��