����3�·ݣ�ِ�`˼��Xilinx���vʷ�ϵ���λȫ��CEO Victor Peng �����ڱ�����ʽ����ِ�`˼���Ƴ������m��(y��ng)Ӌ(j��)�����ƽ�_(t��i)��ACAP��Victor ��ʾ����������Ժ�CPU��GPU�cFPGA ���ᲢՓ�����������h(yu��n)������ߵĮa(ch��n)Ʒ��ACAP���Ը��w���ӏV���đ�(y��ng)�ã������˂���(sh��)�F(xi��n)���ܻ�(li��n)�����(q��)��(d��ng)���m��(y��ng)�����硣��

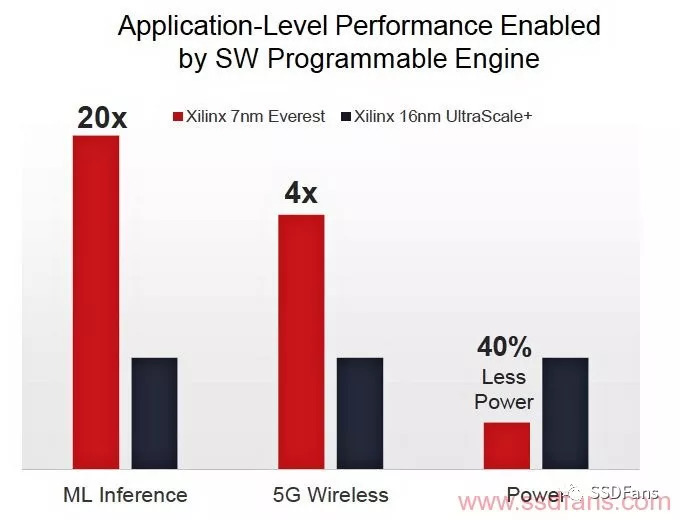

ACAP�����_(t��i)�e�7�{���g(sh��)���ڙC(j��)���W(xu��)��(x��)��Ӌ(j��)�����������16�{��(j��)����20������5Gͨ�ŷ����܉�֧��4���Ď����������ܹ��ıȷ�����Ѓ�(y��u)Խ�ı��F(xi��n)��ACAP��ِ�`˼��˾��Everest �Є�(d��ng)������(n��i)���Q�顰�����ʬ����Є�(d��ng)�����ش�ɹ�����Everest �Є�(d��ng)���ѽ�(j��ng)�v��(j��ng)���꣬Ͷ�Y10�|��Ԫ����(d��ng)��1500�����̎����o(w��)����һ��(g��)�ذ���(j��)���ͮa(ch��n)Ʒ�������f(shu��)��ACAP�Ć�(w��n)������(du��)�I(y��)���(l��i)�f(shu��)��һ�(xi��ng)�ش�ļ��g(sh��)���Ҳ����ِ�`˼��˾�l(f��)��FPGA�ԁ�(l��i)�����Ĺ��̳ɾ͡�

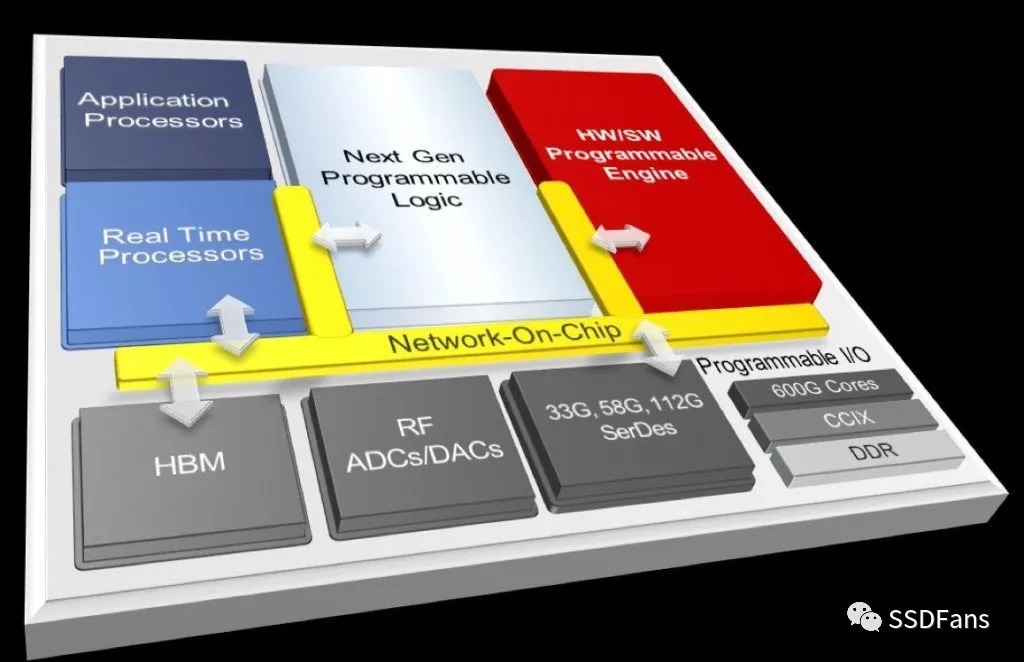

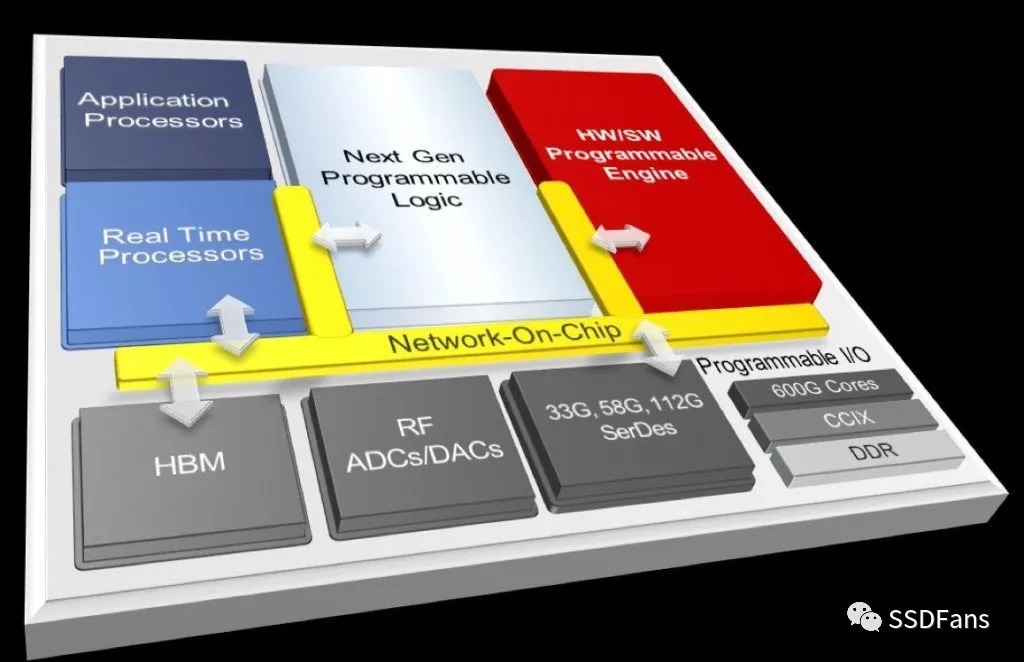

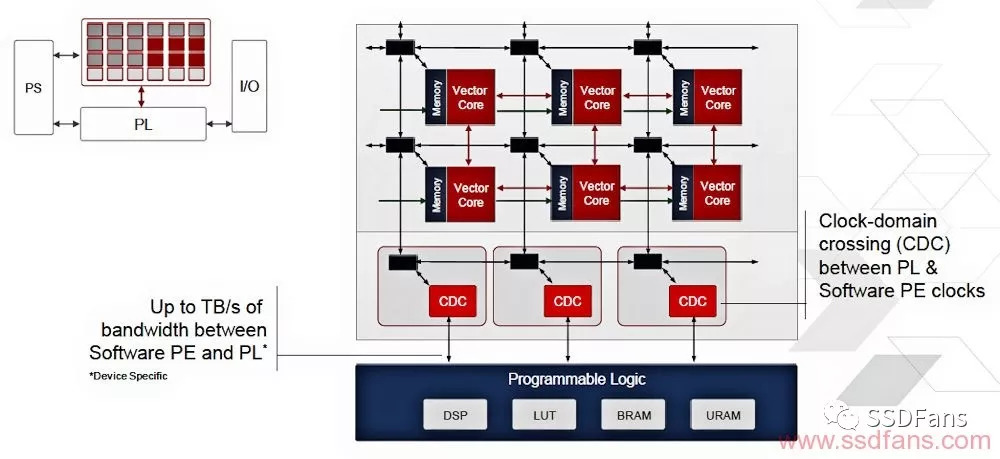

�D1 ACAP�ܘ�(g��u)�D

�ψD�е�����������Ҫģ�K����ij�N��ʽ��Xilinx 16nm Zynq��Virtex��Kintex UltraScale+ϵ���г��F(xi��n)�^(gu��)��������ҪԔ��(x��)�f(shu��)�����@Щģ�K����Arm��(y��ng)�ú͌�(sh��)�r(sh��)̎�������ɾ���߉��HBM���ߎ����惦(ch��)������ʹ�ù�����2.5D�M�b���g(sh��)�B�ӵ�XilinxоƬ�ϵĶѯBʽDRAM��С�RFADC��DAC�Լ�����SerDes�˿ڡ�

�����ǂ�(g��)�tɫģ�K���ǂ�(g��)�i���@�ǹ�˾�����漆֮�赸����һ���֣�����(hu��)�������_(k��i)Everest ��ACAP�a(ch��n)Ʒ�ļ�(x��)��(ji��)���Ķ����O(sh��)Ӌ(j��)�A�ξ��������dȤ�����@�N�I(y��ng)�N���ɵ��`�Ё�(l��i)����һ��(g��)���o(j��)ǰ���������Һ̈́�����?ji��n)W˹���������£�Ŀǰ�@�N�����ܵ��˸߿Ƽ��I(y��ng)�N�ˆT�����������ǵ���A����

8�·��ڼ������၆�ݎ�(k��)�ȵ��Z�e�еġ�Hot Chips 30����(hu��)�h�ϣ����_(k��i)��һ�ɂ�(g��)�[����HW��SW�ɾ�����������ص��漆�����_(k��i)���ڕ�(hu��)�h�ϣ�Xilinx���F(tu��n)���̿��O(ji��n)Juanjo Noguera����һ��Ԕ��(x��)��(b��o)�棬��(bi��o)�}�顰HW/SW�ɾ������棺Everest�(xi��ng)Ŀ���ض��ܘ�(g��u)����Noguera����ʾ��B���S���~���Ӳ����(x��)��(ji��)��ͬ�r(sh��)����������Ȥ�ļ�(x��)��(ji��)��

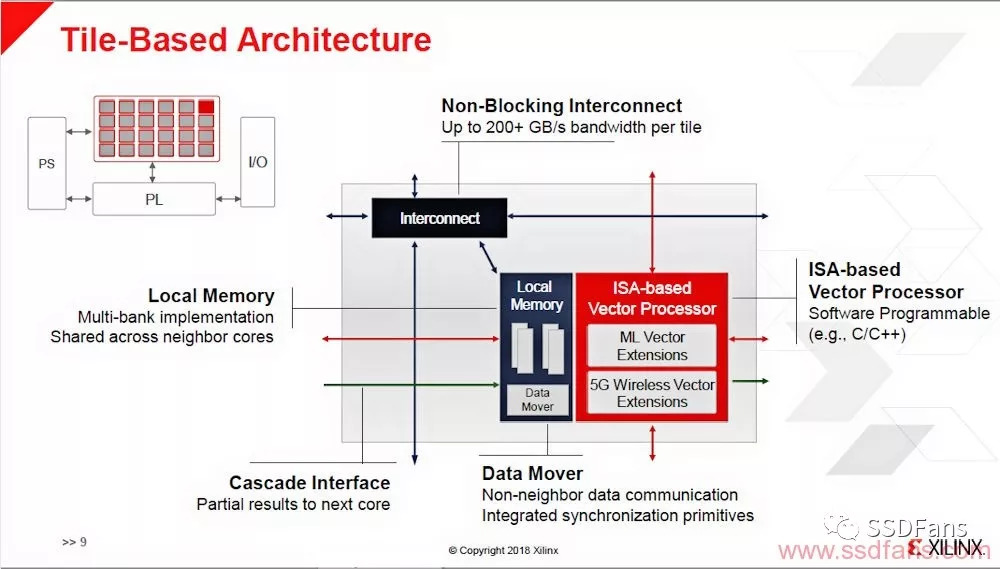

Everest HW/SW�ɾ����������ɴ����ȡ�ܛ���ɾ��̵�VLIWʸ��̎�����M�ɵ�ƽ���У�tiled array���������Զ�NӲ���ɾ��̵ķ�ʽ��B�ӡ�Noguera�J(r��n)�飬VLIWʸ��̎��������̎�����N���c(di��n)���c(di��n)��(sh��)��(j��)��͡�HW/SW�ɾ���������г��F(xi��n)���D�����Ͻǣ������л��B�����Ć�(g��)ģ�K��(x��)��(ji��)λ�ڈD�е����½ǡ�

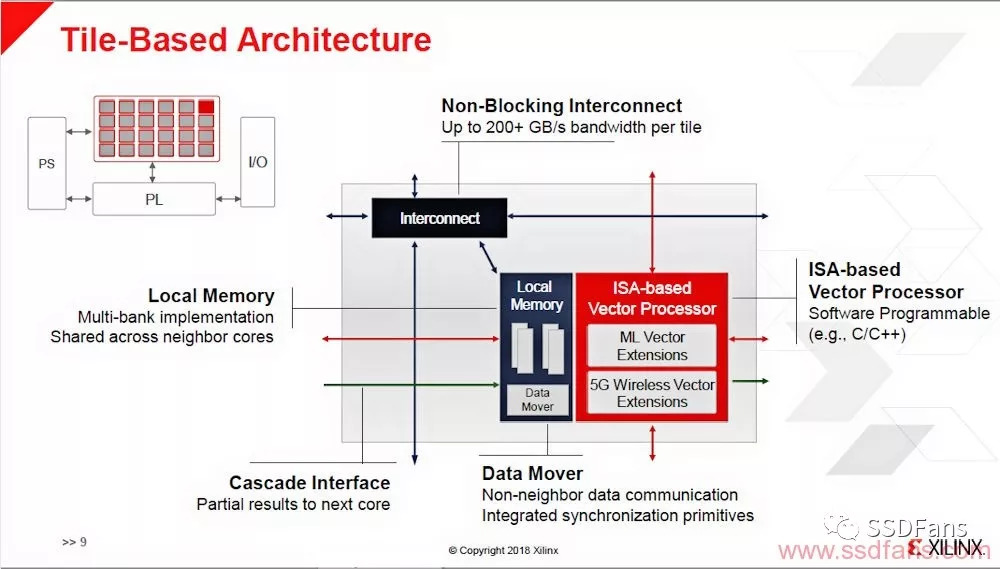

�D2 Xilinx HW/SW�ɾ������挦(du��)Everest�Y(ji��)��(g��u)��Ԕ��(x��)�f(shu��)��

��Everest�O(sh��)Ӌ(j��)�У�HW/SW�ɾ�����������cPS��̎����ϵ�y(t��ng)����PL���ɾ���߉����(d��)��ͨ�š�����е�ÿ��(g��)�K��ܛ���ɾ���VLIW����̎�����͔�(sh��)��(j��)�Ƅ�(d��ng)����DMA�C(j��)�����M�ɡ�

����������N��͵Ļ��B�·ģ�K����һ�N��ͣ��ɈD2�еļtɫС���^��ʾ����ʹ��NSEW�������ϡ��|���������з�����ÿ��(g��)ģ�K�c��������Ă�(g��)����朽�����(l��i)��ƽ�С��p��(sh��)��(j��)�ӿڡ����⣬�D���@ʾ�ľGɫС���^ָ����dž���(j��)(li��n)�ӿڣ����Sһ��(g��)��Ƭ�����ֽY(ji��)��ֱ�ӂ��f�o���������҂�(c��)���ӡ�

�@Щ�̵ġ����ص��c(di��n)���c(di��n)���B��������FPGA��������ڵĶ̾��xLUT-to-LUTͨ�ŵı��ػ��B���伉(j��)(li��n)�ӿ������DSPƬ֮�g���M(j��n)λ�ӿڡ����^(gu��)�@�������ɺϣ���?y��n)��@Щͨ��·����Xilinx�O(sh��)����һֱ�ܳ�Ҋ(ji��n)��

��(du��)��ƽ�������^�L(zh��ng)��ͨ��·����HW/SW�ɾ�������ʹ��200G�ֹ�(ji��)/��ķ��������_����NOC(Ƭ�ϾW(w��ng)�j(lu��))��NOC���ϲ��еı��ػ��B����(g��u)���˿ɾ�������ġ�Ӳ���ɾ��̡��ԡ�

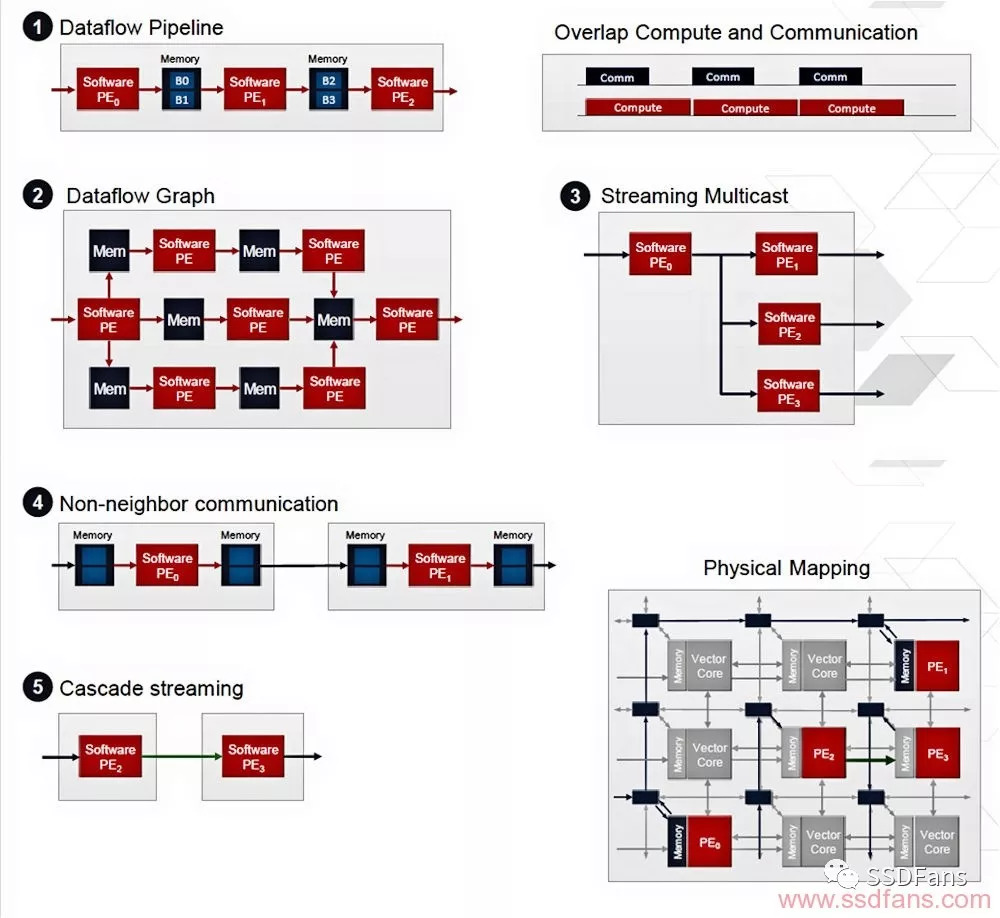

�҂������Զ�N��ʽ�B������̎��K���Ԍ�(sh��)�F(xi��n)��ͬ��̎����С�Noguera���������v��ӑՓ����N��ƵĽY(ji��)��(g��u)���D3�г����@Щʾ����

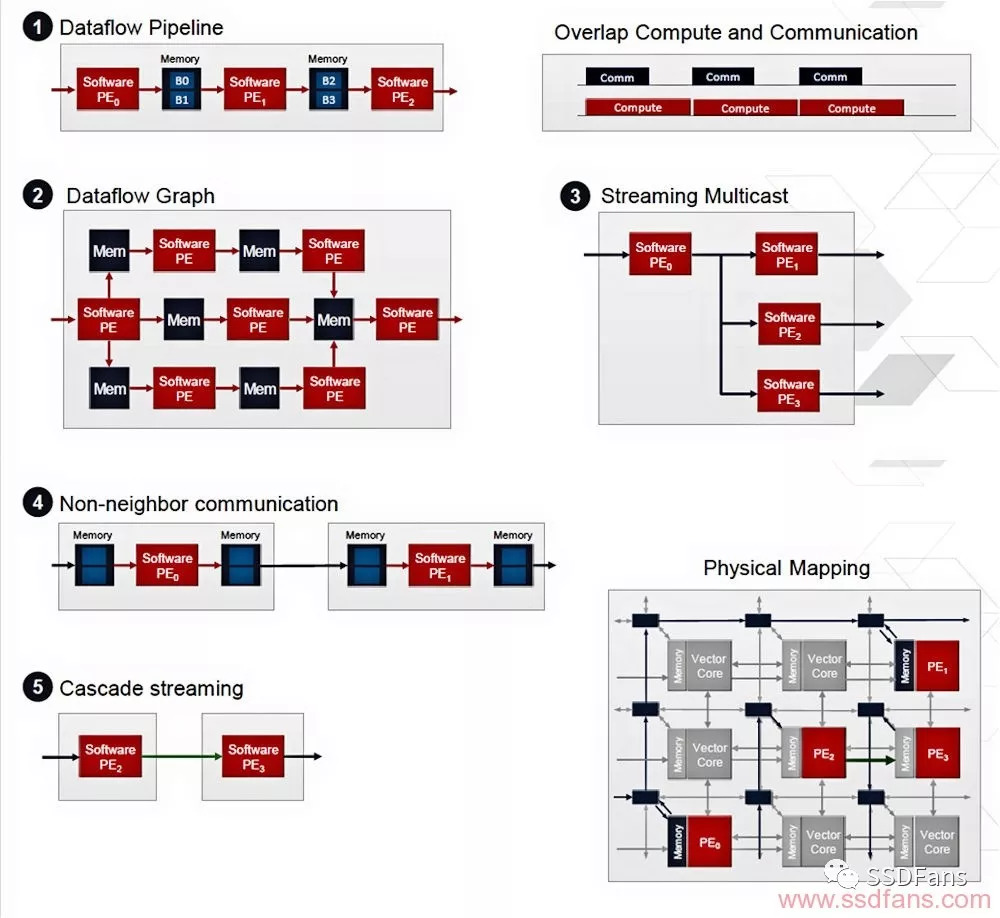

�D3 Everest HW/SW�ɾ�������̎������ʾ��

����1��һ��(g��)��(ji��n)�ε�һ�S����(sh��)��(j��)���ܵ���ÿ��(g��)̎��K̎�����Ĕ�(sh��)��(j��)��һ���֣�Ȼ��ͨ�^(gu��)����(n��i)�澏�_�^(q��)���Y(ji��)�����f����һ��(g��)�K������2��һ��(g��)��(sh��)��(j��)���D��ԓ��(sh��)��(j��)���D���Կ����ǔ�(sh��)��(j��)���ܵ��Ķ�S�汾���ı��|(zh��)���v������Ȼ�ǹܵ������^(gu��)���ڶ���(g��)�S�����\(y��n)�еġ�����3����NOC���Y(ji��)����һ��(g��)̎��Kͬ�r(sh��)�ಥ���ɂ�(g��)�����(g��)���m(x��)�K������4ʹ��ݔ���ݔ���惦(ch��)�����_�^(q��)��(l��i)ƥ���B����NOC�ϵĉK�IJ��̎�����ʡ�����5����ʹ�ü�(j��)(li��n)�ӿڌ����g�Y(ji��)����һ��(g��)�K���f����һ��(g��)�K���������������YԴ��

�@ֻ���傀(g��)����ʾ����ʹ���@�N�µ�̎���YԴ���Ԅ�(chu��ng)��������̎�����ã�����߀��һЩ�����Ԅ�(d��ng)���Ŀ��g���Ժϳɺ̓�(y��u)�����ã��ԝM������ܡ��߹��ʵ�Ŀ��(bi��o)����(d��ng)Ȼ���@Щ���B����Ҳ���ԽM��ʹ�á�

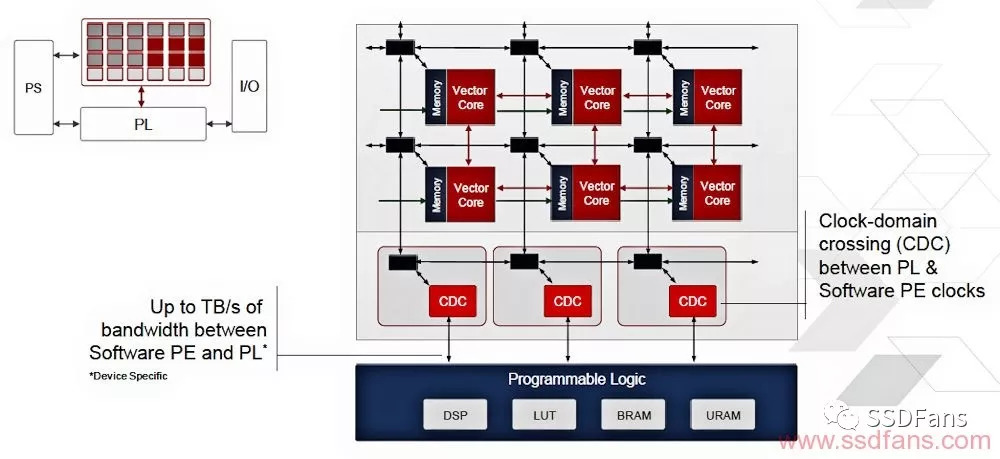

HW/SW�ɾ�������Ĺ��ܿ���ʹ��Everest��Ƭ��PL�M(j��n)�ДU(ku��)չ��ԓP(y��ng)Lͨ�^(gu��)����(g��)NOC��(ji��)�c(di��n)��CDC���r(sh��)��棩���_�^(q��)�B�ӵ�HW/SW�ɾ��������NOC�ϣ���D4��ʾ�����@Ȼ��ԓ�ܘ�(g��u)��ҪCDC���_�^(q��)����?y��n)�HW/SW�ɾ��������PL�ĕr(sh��)����ʲ�ͬ�����^(gu��)�����\(y��n)���ٶȑ�(y��ng)ԓ����(hu��)׃������

�D4 HW/SW�ɾ��������NOCͨ�^(gu��)����(g��)NOC��(ji��)�c(di��n)�͕r(sh��)��澏�_�^(q��)�B�ӵ��O(sh��)��Ŀɾ���߉��

��D��ʾ��Everest��HW/SW�ɾ������棨�D�пs����PE�����c��PL֮�g�Ļ��B��������Tbytes/sec����(j��)���@����(d��o)���S��ϵ�y(t��ng)�ܘ�(g��u)�����ò�����˼�������P(gu��n)��̎�����wϵ�Y(ji��)��(g��u)�ļ��O(sh��)��

�҂�����ʹ���B�ӵ�PL�Զ�N��ʽ����(qi��ng)HW/SW�ɾ�����������������磬����ʹ��PL��RAM��Ё�(l��i)��������̎��K��(du��)PL�е�Ƭ��SRAM (BRAM��UltraRAM)�K���L��(w��n)��Ҳ����ʹ��PL��(l��i)��(sh��)�F(xi��n)Ӳ���������������ԱȉKʸ���������؈�(zh��)���ض���Ӌ(j��)�㡣Noguera���hʹ��PL��tile��(chu��ng)����ISA�U(ku��)չ���������](m��i)��Ԕ��(x��)�f(shu��)����

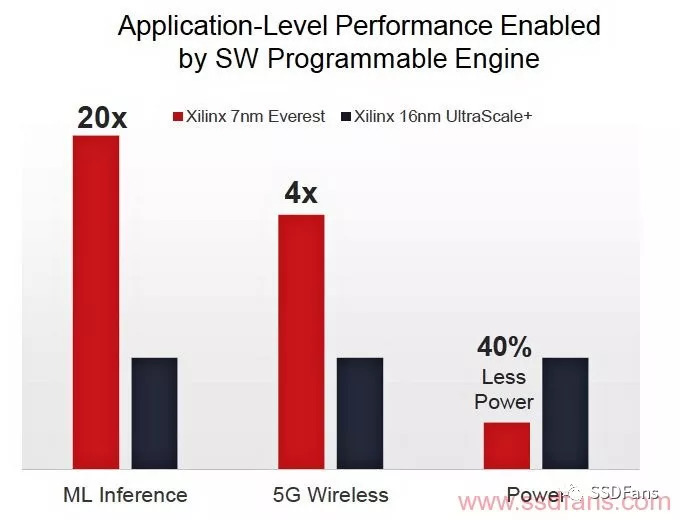

�C(j��)���Z(y��)��������5G�o(w��)����̖(h��o)̎�������ܽY(ji��)���o�����������ӡ�����D5��ʾ��

�D5 HW/SW�ɾ�����������(du��)�ڿɾ���߉��(sh��)�F(xi��n)�ĽY(ji��)����

ֵ��ע�����ML���C(j��)���Z(y��)�ԣ�������20�����M(j��n)����(d��ng)�漰��ML����r(sh��)��F(xi��n)PGA�ѽ�(j��ng)�ஔ(d��ng)�죬��?y��n)������?j��)���漰�S��˷��ͼӷ���FPGA�еĔ�(sh��)��ǧӋ(j��)��DSPƬ���Կ��ٵ؈�(zh��)���@ЩӋ(j��)�㣬����HW/SW�ɾ��������ƺ����졣Noguera�f(shu��)��5G�o(w��)��̎���е�4�����M(j��n)Ҳ����Ҫ����?y��n)��@��ζ�������ʬ���ܘ�(g��u)�����_(d��)��2G./sec�Ă�ݔ���ʡ�

��Noguera���v��Ć�(w��n)��h(hu��n)��(ji��)�У� (t��ng)�������һЩԔ��(x��)�Ć�(w��n)�}����һ��(g��)��(w��n)�}���P(gu��n)��HW/SW�ɾ�������ĕr(sh��)����ʡ�Noguera�Ļش��ǣ���߀����ֱ�ӻش��@��(g��)��(w��n)�}��������ԇ�Dͨ�^(gu��)���������̎��2G./sec��5G��ݔ�����ʁ�(l��i)�g�ӻش����f(shu��)��HW/SW�ɾ�������̎�����Ĺ����l�ʌ��ǡ�ǧ��(j��)����

��һ��(g��)��(w��n)�}�漰HW/SW�ɾ�����������е�ģ�K��(sh��)��������ÿ��(g��)HW/SW�ɾ��������Ќ��Д�(sh��)ʮ����(sh��)�ق�(g��)ģ�K���@ȡ�Q���O(sh��)�䘋(g��u)�ɡ�ACAP�O(sh��)���HW/SW�ɾ����������Д�(sh��)�ق�(g��)ʸ��̎����������������Ҏ(gu��)ģ���л����@��(g��)�����c����FPGA����(y��ng)�̣�����Xilinx���ڏV�����O(sh��)������Ќ���ͬ��(sh��)�����YԴ���õ���(g��)�ɆT�еķ�ʽ�dz�һ�£����������_(d��)��Xilinx�_(k��i)�l(f��)ACAP�O(sh��)��������D��

Ȼ������һ��Everest�O(sh��)��߀�](m��i)�г���(l��i)���@һ��̱��Ե�Ӌ(j��)�����ڽ�����Щ�r(sh��)��?q��)��F(xi��n)��ͬ�r(sh��)���߂�(g��)�漆���赸߀���^�m(x��)��Noguera���Z���ڽ�����Щ�r(sh��)����ʥ�����������ͷ��m�˸��e�е�Xilinx�_(k��i)�l(f��)��Փ������¶���༚(x��)��(ji��)��